体系结构复习5

第5章 存储系统

存储器的分类和主要特点

Ø半导体存储器

Ø磁表面存储器

Ø光盘存储器

存储器存取方式:Ø随机存取存储器(RAM)Ø顺序存取存储器(SAM)

利用局部性原理:

. 以最便宜技术提供尽可能多的存储空间

. 以最快的技术提供访问

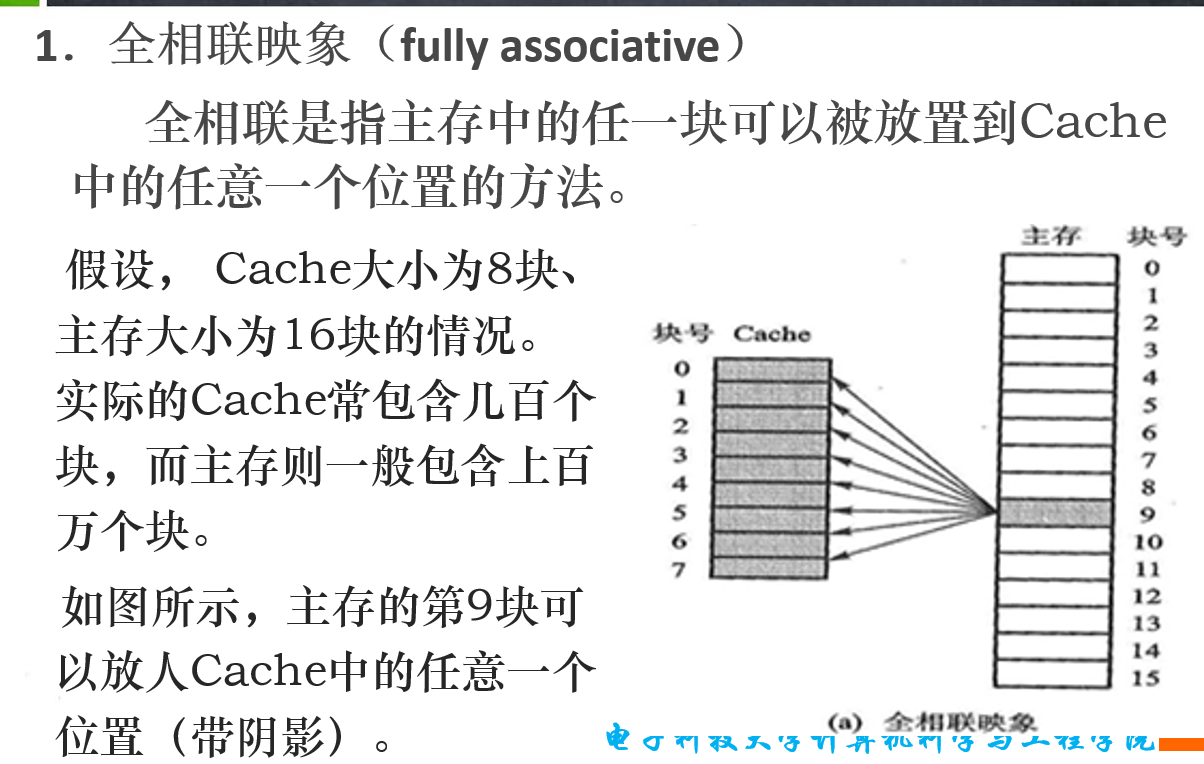

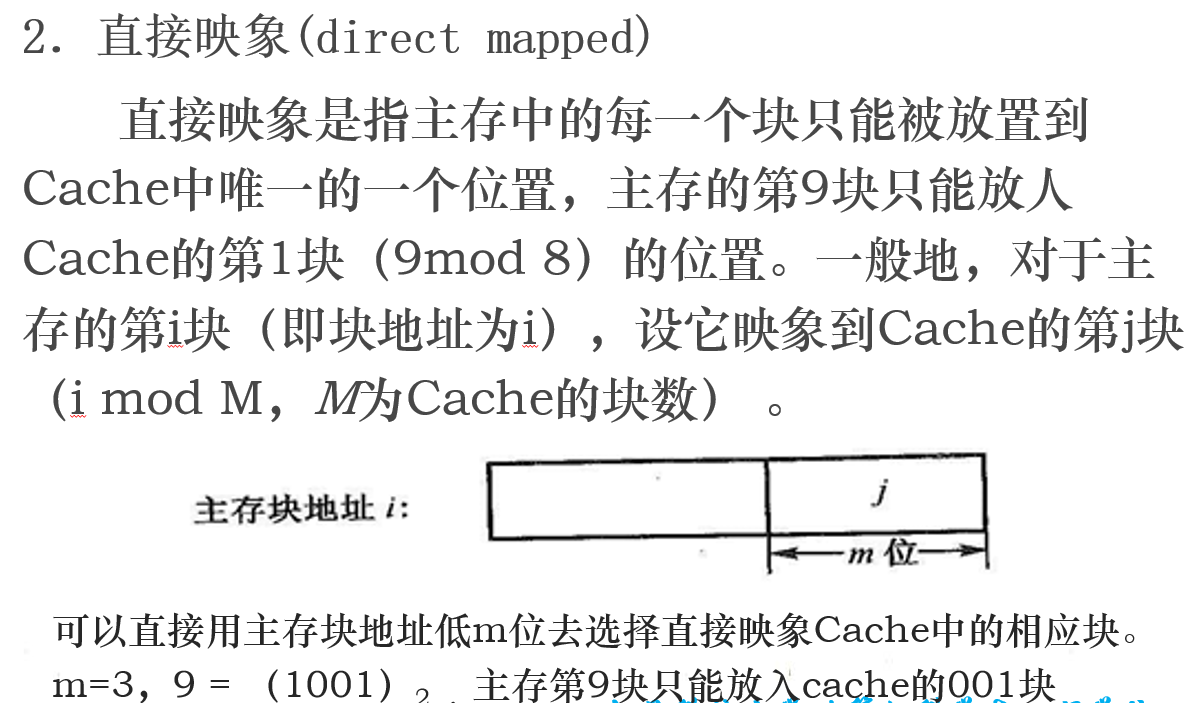

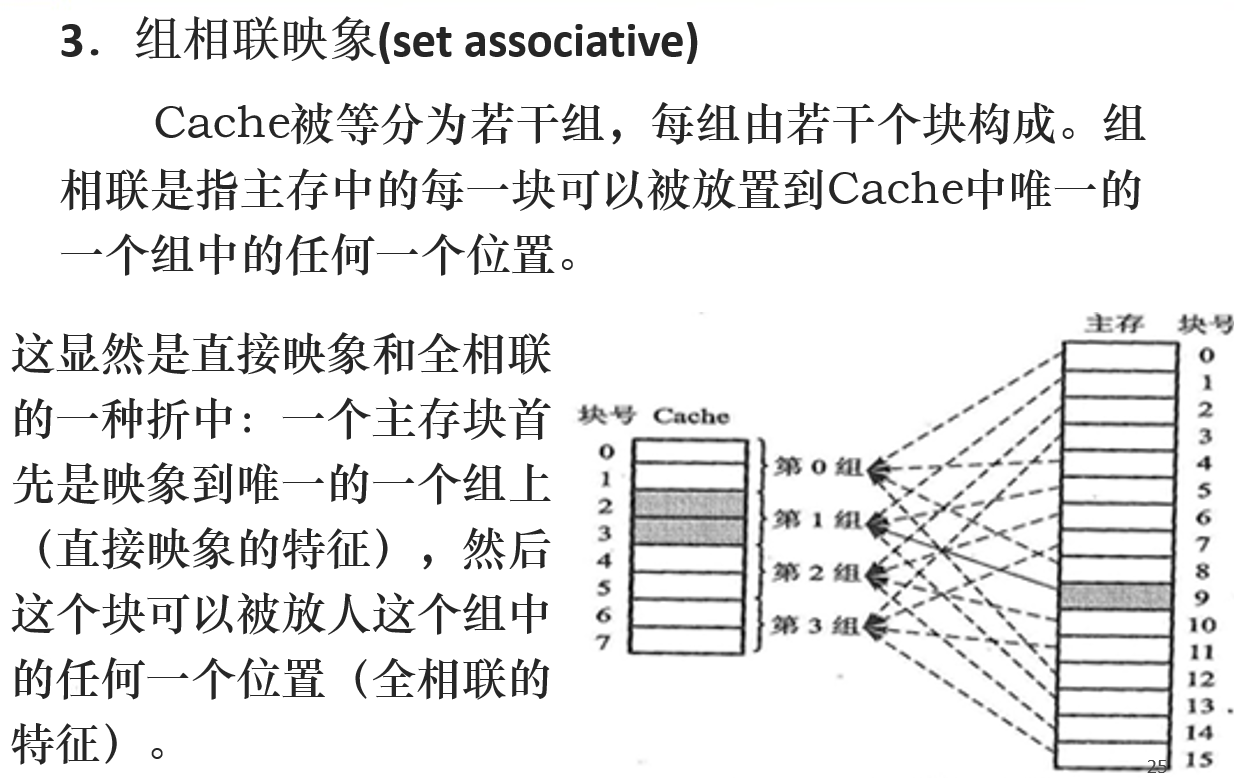

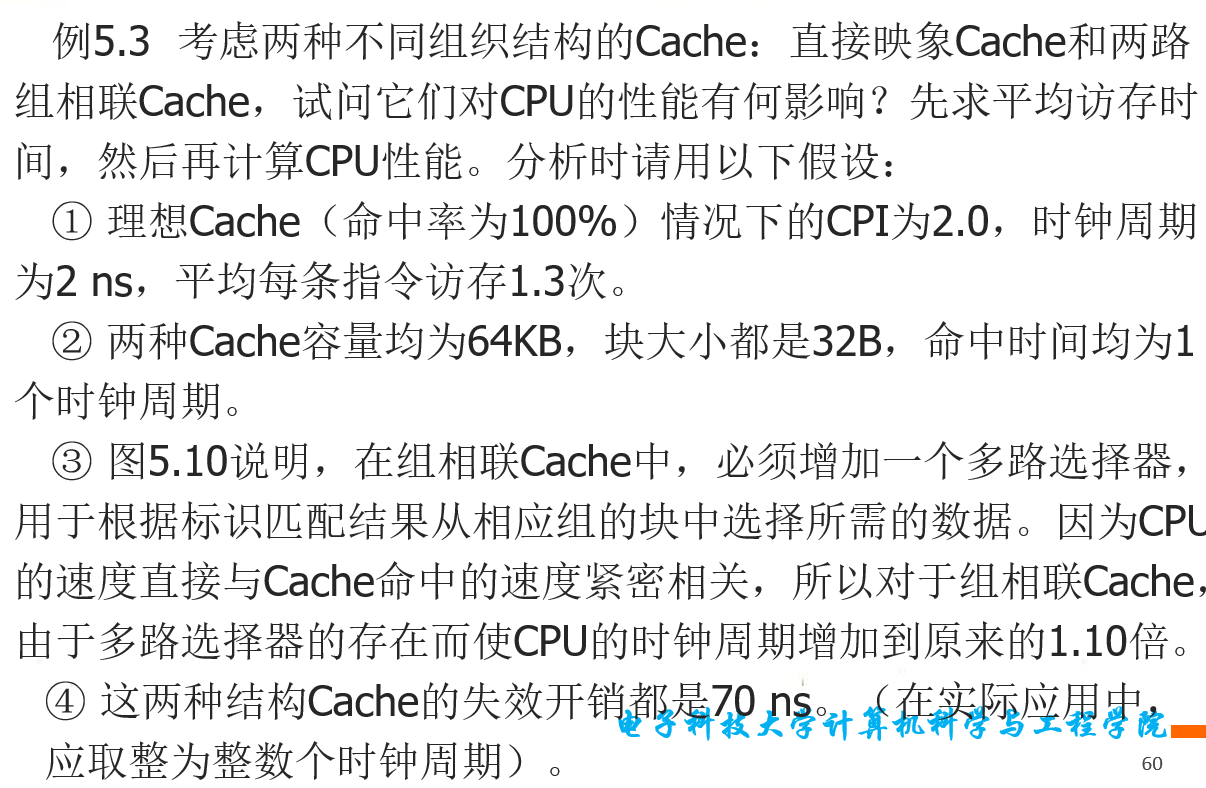

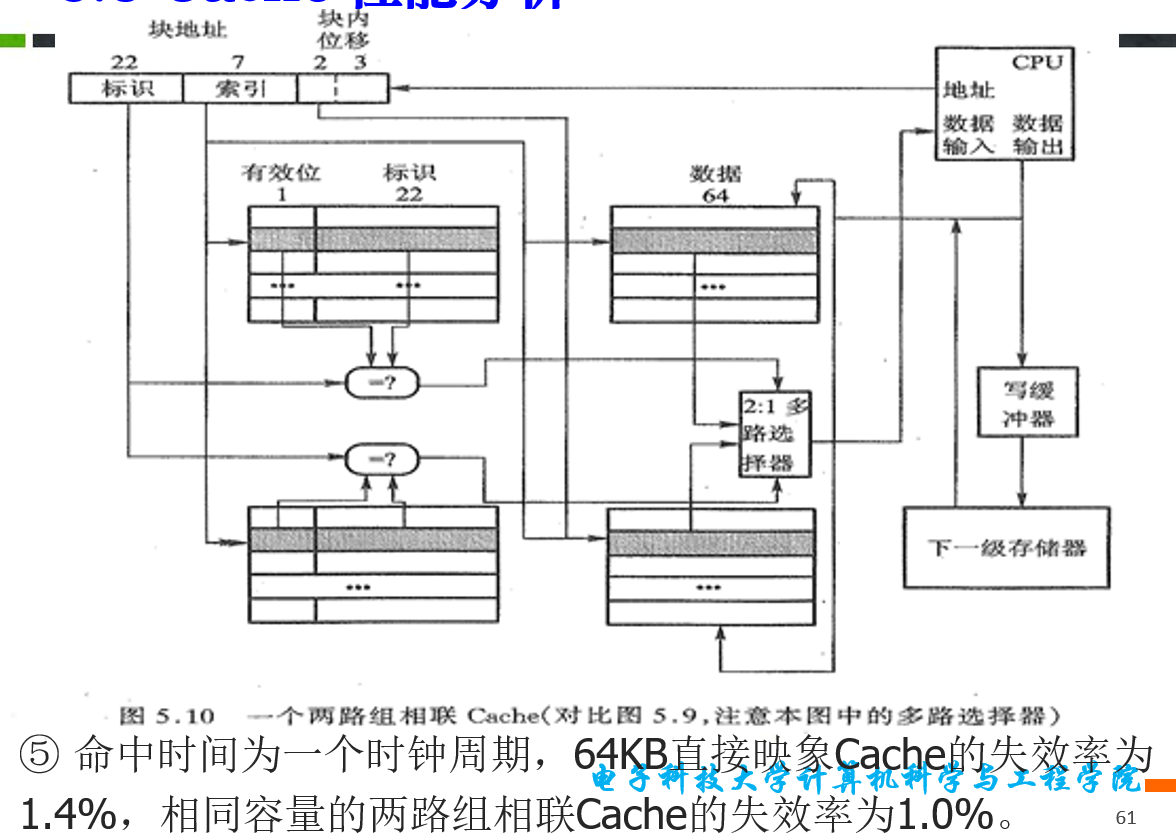

Cache的三种映像关系:全相联、直接映像、组相联

主存地址Tag、Index、块内偏移三个字段的计算

Cache块的替换策略

Cache的读写过程

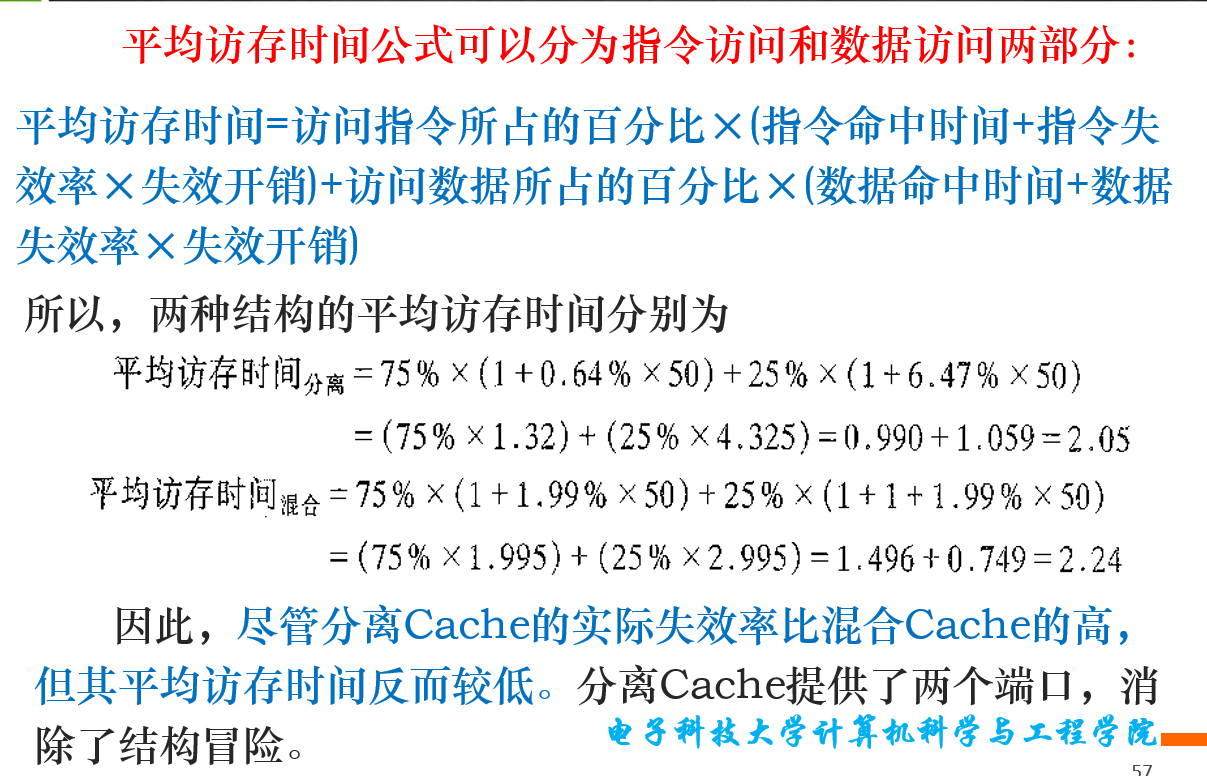

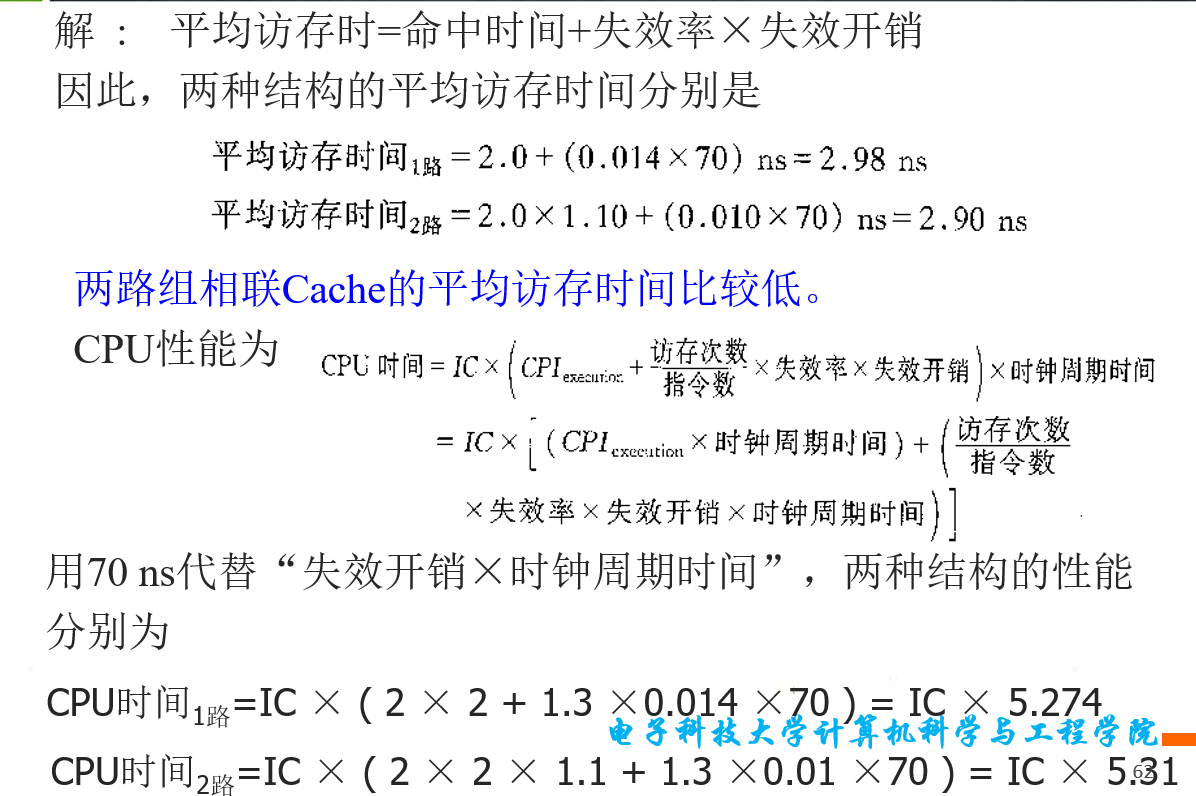

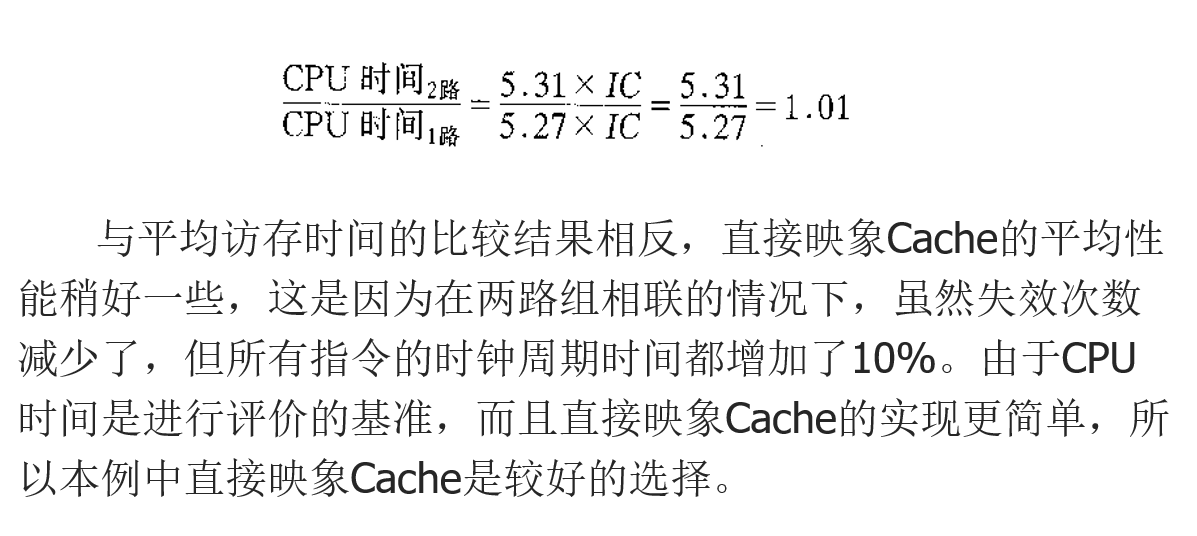

平均访存时间和CPU时间的计算

Cache失效率的类别,以及每种失效率的解决方法有哪些

按照产生失效的原因不同,可以把失效分为以下3类(简称为“3C”):

强制性失效(Compulsory Miss):当第一次访问一个块时,该块不在Cache中,需从下一级存储器中调入Cache,这就是强制性失效。这种失效也称为首次访问失效。

解决方法:减少强制性失效,可以增加块的大小。

容量失效(Capacity Miss):如果Cache容纳不了一个程序执行所需要的所有块,将会发生容量失效(还会发生强制失效),某些块将被丢弃,随后再被调入

解决方法:要减小容量失效,可以增大Cache的容量。

冲突失效(Conflict Miss):在组相联或直接映象Cache中,若太多的块映象到同一组(块)中,则某一个块被放弃,之后再重新调入,这时发生了冲突失效。

解决方法:冲突失效似乎是最容易减少的,只要采用全相联,就不会发生冲突失效。

1 增加块容量:

• 减少了强制性失效,利用了空间局部性;

• 减少Cache中块的数目,所以有可能会增加冲突失效。在Cache容量较小时,甚至还会增加容量失效。

2 提高相联度

• 8路组相联在降低失效率方面的作用已经基本和全相联一样有效。也就是说,采用相联度超过8的方法实际意义不大。

• 2:1 Cache经验规则,它是指容量为N 的直接映象Cache的失效率与容量为N/2的两路组相联Cache的失效率差不多相同

增加块大小的方法会在降低失效率的同时增加失效开销,而提高相联度则是以增加命中时间为代价。

3 增大Cache容量

4 编译器优化

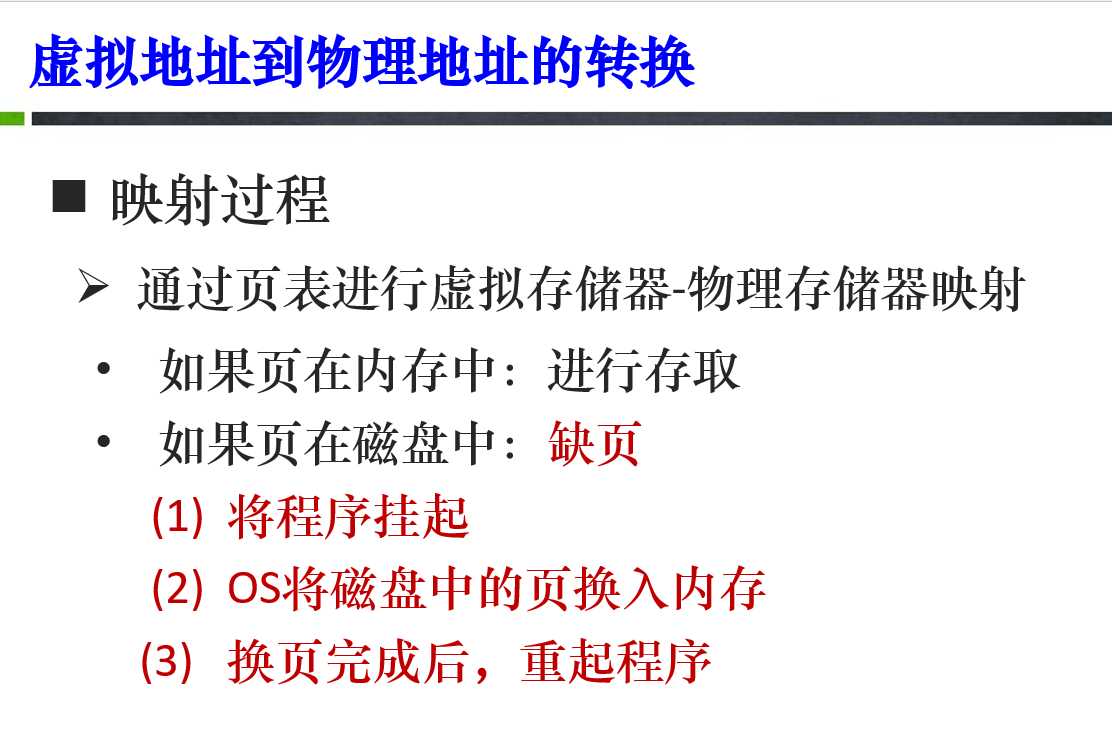

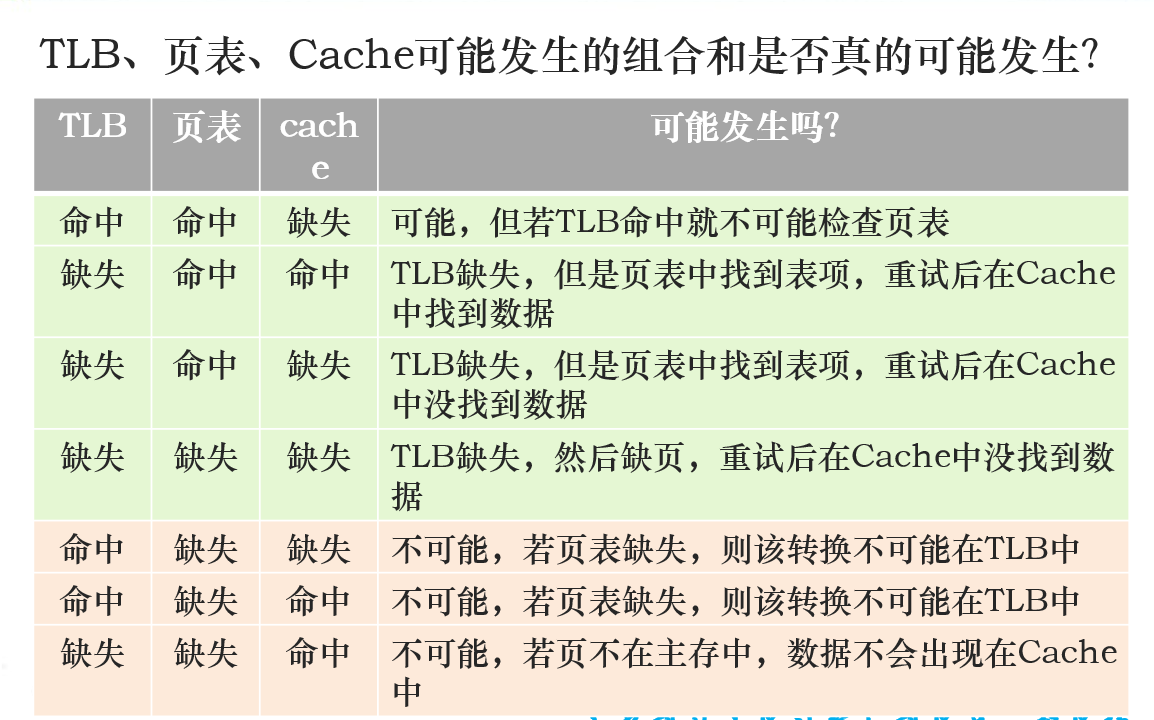

虚拟地址到物理地址的转换过程,TLB表的原理和作用,与Cache的关系,访存时间的最好情况和最坏情况的判断

虚拟存储器 又称虚拟内存,将主存的用作辅助存储器(磁盘)高速缓存的技术。即将磁盘的一部分当作内存使用。

采用虚拟存储器的目的 Ø更有效地共享处理器和主存 Ø可以运行超过主存容量的程序

虚拟地址到物理地址的转换:

过程:

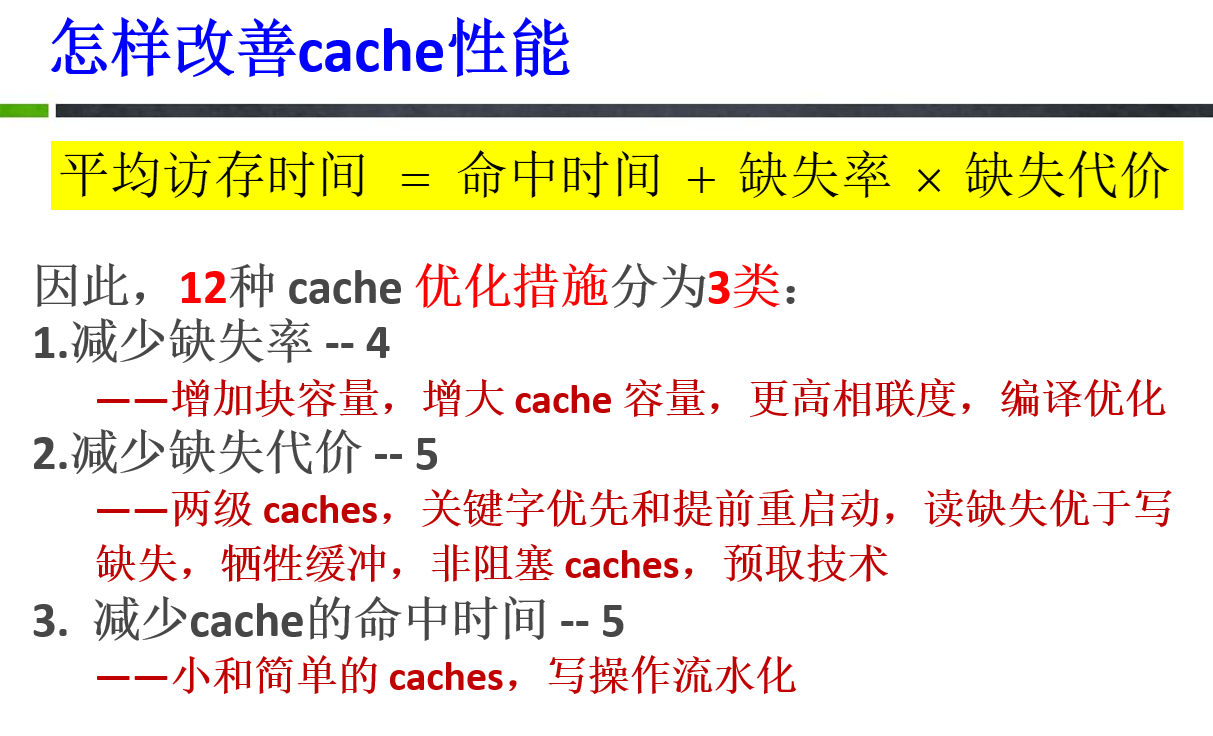

通过页表进行虚拟地址到物理地址的映射。如果页在内存中,直接存取;如果页在磁盘中,则触发缺页异常。

转换步骤:- 处理器产生虚拟地址。

- 页表将虚拟页号映射到物理页号,并加上页内偏移,生成物理地址。

- 如果有效位为0,表示缺页,操作系统处理缺页异常,将所需页面加载到内存。

TLB加速转换:

虚拟地址转换通常需要访问页表,耗费两个存储周期(一个获取物理地址,一个访问数据)。通过TLB(Translation Lookaside Buffer),缓存最近的虚拟地址和物理地址映射,命中时只需一个存储周期。

- TLB表的原理和作用:

- 原理:

- TLB 是一种专门的高速缓存,存储最近使用过的页表项。

- 对虚拟地址的转换,通过查询TLB快速获取物理地址。如果TLB命中,则直接用物理地址访问内存;若TLB缺失,则查询页表补充TLB。

- 作用:

- 加速地址转换过程,减少页表访问次数。

- 提高虚拟存储器的性能。

- 原理:

- TLB与Cache的关系:

- 两者结合:

- TLB 用于虚拟地址到物理地址的转换。

- Cache 用于加速数据访问(物理地址)。

- 访存流程:

- 处理器生成虚拟地址,TLB将其转换为物理地址。

- 使用物理地址在Cache中查找数据。

- 关系特点:

- TLB 负责地址转换,Cache 负责数据缓存。

- TLB 命中与Cache命中分别决定访存时间的长短。

- 两者结合:

- 访存时间的最好与最坏情况:

- 最好情况:

- TLB命中且Cache命中,访问数据只需1个存储周期。

- 最坏情况:

- TLB缺失、页表缺页、Cache未命中。

- 涉及操作:处理缺页异常,加载页面,更新TLB和Cache,最差可能需访问磁盘。

- 最好情况: